Hindawi Publishing Corporation Journal of Sensors Volume 2016, Article ID 1082454, 9 pages http://dx.doi.org/10.1155/2016/1082454

### Review Article

# **EMI Susceptibility Issue in Analog Front-End for Sensor Applications**

#### Anna Richelli

Department of Information Engineering, University of Brescia, Via Branze 38, 25123 Brescia, Italy

Correspondence should be addressed to Anna Richelli; anna.richelli@ing.unibs.it

Received 22 July 2015; Revised 9 November 2015; Accepted 15 November 2015

Academic Editor: Fernando Benito-Lopez

Copyright © 2016 Anna Richelli. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

The susceptibility to electromagnetic interferences of the analog circuits used in the sensor readout front-end is discussed. Analog circuits still play indeed a crucial role in sensor signal acquisition due to the analog nature of sensory signals. The effect of electromagnetic interferences has been simulated and measured in many commercial and integrated analog circuits; the main cause of the electromagnetic susceptibility is investigated and the guidelines to design high EMI immunity circuits are provided.

#### 1. Introduction

Current trends in consumer electronics highlight an increased interest in ubiquitous electronic devices. This is especially true in the field of sensors which can enable a variety of applications including interactive environments for medicine [1–5], military target tracking, automotive [6, 7], and environmental monitoring networks [8, 9]. Analog circuits still play a crucial role in sensor signal acquisition due to the analog nature of sensory signal: they are indeed widely used in the sensor readout front-end, since it directly interfaces the sensor [10–12]. Analog circuits are indeed employed for signal conditioning and conversion, generation of bias and reference voltages and currents, and systems interfacing.

In recent years, integrated sensor systems have become widely commercially available. These systems usually contain microsensor array and sensor electronics [13–15]. When the sensor integration is not feasible due to economical or technical reasons, off-chip sensors may also be used. Nevertheless, the common feature is that the sensor electronics, sensor signal conditioning, processing, and conversion, generation of necessary bias, and reference voltages as well as currents, control, clock signals, and sensor system interface are located on a single chip or a chip set.

In the literature, much attention is paid to many aspects, such as the resolution of a sensor system. The final limit

of the resolution is represented by the sensor-input referred noise. This noise may contain contributions of the sensor itself and of sensor electronics and therefore a lot of attention has been paid in noise reduction techniques to improve the sensor resolution.

Another important issue is that the noise can be generated by neighboring circuits and enter the system due to crosstalk, which can be either capacitive (due to stray capacitances) or conductive and inductive, through the power supply rails.

In the literature the effect of the noise and the crosstalk have been widely investigated and many noise reduction techniques and guidelines are depicted and provided [16].

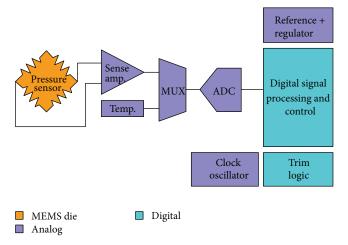

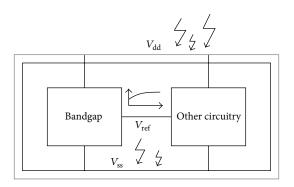

However, when several analog and digital subsystems are required to coexist on the same chip, eventually sharing the same power sources, as in the sensor applications, another issue is becoming more and more important: the immunity to electromagnetic interferences (EMIs). As an example of this scenario, in Figure 1 a schematic view of a pressure sensor, with highlighted analog and digital blocks, is shown.

In such a system, EMI may arise from external circuits and from subsystems integrated on the same die, spreading through the supply lines and the I/O interconnections.

In the sensor design the influence of EMI is generally not treated explicitly or even neglected.

This paper describes the effect of the electromagnetic interferences in analog circuits, widely used in the sensor interface: general-purpose operational amplifiers and voltage

FIGURE 1: Example of a sensor circuit, with highlighted analog and digital blocks, eventually sharing the same chip and power supplies.

references. Measurement results of the EMI susceptibility in commercial devices are provided and the state-of-theart design of high EMI immunity amplifiers and voltage references is depicted. In particular, in Section 2, the problem of electromagnetic interferences will be briefly introduced and the results of measurements performed on several commercial amplifiers victims of EMI will be provided; in Section 3, the design of high-immunity amplifiers will be depicted and in Section 4 the guidelines to design high EMI immunity voltage references will be provided and finally conclusions will be drawn.

## 2. The Problem of Electromagnetic Interferences in the Analog Circuits

Electromagnetic interference (EMI) effects may arise from a wide class of sources (cellular telephones, CD players, laptop computers, etc.): as an example, aircraft may be susceptible to electronic interferences because of their reliance on radio communication and navigation systems whose electromagnetic spectrum ranges from 10 kHz (navigation systems) to above 9 GHz (weather radar). Furthermore, the massive introduction of electronics in automotive may cause a number of problems: cellular telephone transmitters, for instance, can induce disturbances in braking systems (ABS). EMI may arise from inside the automobile as well: alternators, ignition systems, switching solenoids, and electric starters are potential sources of such disturbances. Furthermore, due to the high density of components packed on printed circuit boards as well as the increasing speed of mixed analog/digital circuits, IC designers have to consider EMI during design phase. Neglecting these aspects may lead to failures on integrated circuits induced by spurious signals, including EMI at frequencies outside the working bandwidth of the circuit. Two different interferences should be considered, depending on the way they reach the circuits: the distributed ones and the conveyed ones. However, considering the chip

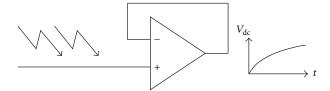

FIGURE 2: Effect of EMI conveyed into the input pin of an operational amplifier in voltage follower configuration.

size and the frequencies, the most important are the conveyed ones.

In recent years, the effects of the conveyed EMI were carefully investigated both theoretically and experimentally in order to find possible prevention methodologies [17–25], in particular, in high-performance digital/analog ICs that may include several operational amplifiers. The most sensitive circuits to EMI are, indeed, the analog ones and, among them, the OpAmps.

In order to investigate the EMI effects on a generic amplifier, the interfering signals are often represented by a sinusoidal waveform generated with zero DC mean value superimposed on the pins connected to long wires (long wires, indeed, act as antennas for EMI) [18, 20]. The amplifier is in the voltage follower configuration, as reported in the literature [21-23] and shown in Figure 2, since it is the worst case condition, because the input differential pair experience the largest disturbance. One of the most undesirable effects of interferences is the shift of the output DC mean value (offset) that may asymptotically force the amplifier to saturation [23– 25]. Furthermore, among all the possible interfering signals the ones superimposed on the input pins of the operational amplifier are the most difficult to prevent [24, 25]. This is due to the fact that the adoption of external filters may modify the original input signals which are often very weak. As far as the power pins are concerned, easy filtering can prevent the dangerous DC offset from being formed.

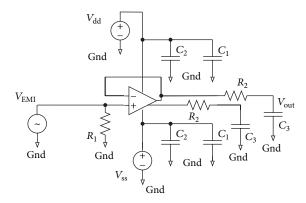

The maximum measured EMI induced voltage offset of some commonly used commercial amplifiers is listed in Table 1: all the amplifiers were connected in a voltage follower configuration and the interfering sinusoidal signal, applied to the noninverting input pin, had an amplitude of 1V at a frequency ranging from 100 kHz up to 1 GHz. The power supply was set to 12 V. Several samples of the most widely used technologies are listed: bipolar, jfet, and CMOS. The amplifiers were measured on a simple PCB following the schematic illustrated in Figure 3. A 33120A Hewlett-Packard RF function generator has been used with  $50 \Omega$  matching load to generate the EMI; the power supply and the biasing voltages were supplied by E3630A Hewlett-Packard power supply. The board interconnections were designed as short as possible along with straight paths and ground shields, in order to minimize all the undesired signals arising from the measurement setup itself. The resistor  $R_1$  in Figure 3 is used for the matching load, while  $C_1$  and  $C_2$  are power supply filters of, respectively,  $100 \, \text{nF}$  and  $10 \, \mu\text{F}$ ; furthermore, the output pin is connected to an RC ( $R_2 = 1 \text{ k}\Omega$ ,  $C_3 = 1 \text{ nF}$ ) filter with cut-off frequency of 160 kHz in order to evaluate

| Amplifier | Technology      | Voltage offset   | Critical frequencies                |

|-----------|-----------------|------------------|-------------------------------------|

| UA741     | BJT             | 650 mV           | 0.1 MHz-3 GHz                       |

| AD705     | BJT             | $350\mathrm{mV}$ | $0.3\mathrm{MHz}$ – $1\mathrm{GHz}$ |

| NE5534    | BJT             | $360\mathrm{mV}$ | $3\mathrm{MHz}$ – $0.6\mathrm{GHz}$ |

| OPA177    | BJT             | $360\mathrm{mV}$ | 0.6 MHz-0.1 GHz                     |

| OP176     | JFET In/BJT Out | $200\mathrm{mV}$ | 3 MHz-1 GHz                         |

| MC33181   | JFET In/BJT Out | 210 mV           | 6 MHz-0.6 GHz                       |

| CA3140    | CMOS In/BJT Out | $350\mathrm{mV}$ | $0.1\mathrm{MHz}$ – $1\mathrm{GHz}$ |

| ICL7611   | CMOS            | 380 mV           | 0.3 MHz-0.3 GHz                     |

FIGURE 3: Schematic of the PCB used to characterize the EMI susceptibility of several commercial amplifiers.

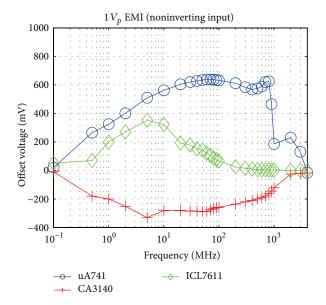

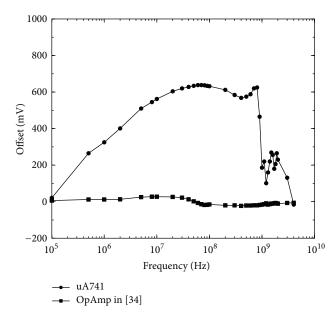

the mean voltage that easily and accurately quantifies the DC shift due to EMI effects. Clearly, the measured offset voltage is significant and can cause failures (due to debiasing) in the circuits connected to the OpAmps. Finally, to have an easy view of the EMI effect in some commercial amplifiers, the induced offset in mV is plotted in Figure 4.

#### 3. The Design of High EMI Immunity OpAmps

As stated above, among all the possible interfering signals the ones superimposed on the input pins are the most difficult to prevent.

When electromagnetic interference is injected in the input pins of an operational amplifier, the latter generates an EMI induced offset voltage because of the nonlinear distortion taking place in the input differential pair [20].

This behavior is correlated to the slew rate asymmetry and to the unequal parasitic capacitances which play a significant role, respectively, at low-medium frequencies and at high frequencies, outside the working bandwidth [20, 24, 25].

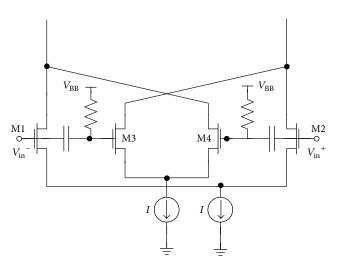

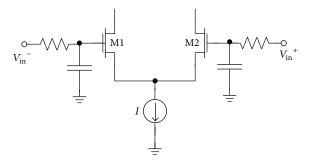

Recently, some solutions have been proposed to intrinsically improve the immunity of the amplifiers to EMI signals arising from the input pins. For example, in [26] the design of an input stage is reported, based on a double cross-connected differential pair along with a simple high-pass filter, as shown in Figure 5. The cross-connected differential pair becomes active only in the passband of the RC high-pass filter. More recently, in [27], a comparison between the architecture

FIGURE 4: Measured EMI induced offset in uA741, CA3140, and ICL7611.

FIGURE 5: The high EMI immunity cross-coupled differential pair with high-pass filter proposed in [26].

proposed in [26] and a simple differential pair with an RC low-pass filter, as the one in Figure 6, has been illustrated.

However, as stated above, a filter may modify the response of the amplifier and, thus, it can just operate at out-of-band frequencies, while the EMI effects are relevant also at lowmedium frequencies.

Another solution has been proposed in [28], based on a double differential pair: in this architecture the nominal differential pair is bootstrapped using bulk biasing: the use of a bootstrapped differential pair results in an advantageous effect of the parasitic capacitances presented at the common source of the differential pair. In the design example shown in [28], the bootstrapped differential pair exhibits an EMI immunity two orders of magnitude larger than the classic differential pair. Nevertheless, following this approach, only

FIGURE 6: A simple RC filter on the input differential pair, as the one discussed in [27].

a P-type differential input stage can be fabricated in a standard CMOS technology: the N-type stage requires, indeed, a triple-well technology due to the bulk biasing.

EMI resistant differential pairs are proposed in other recent works as well [29, 30]; among them a simple and interesting approach to enhance the EMI immunity is based on an RC filter connected to an auxiliary differential pair, as proposed in [31–33]. The RC filter on the auxiliary differential pair introduces indeed a pole-zero doublet and allows for a larger GBW product and a better phase margin, compared to the RC filter connected to the main differential pair, still showing an improved EMI immunity.

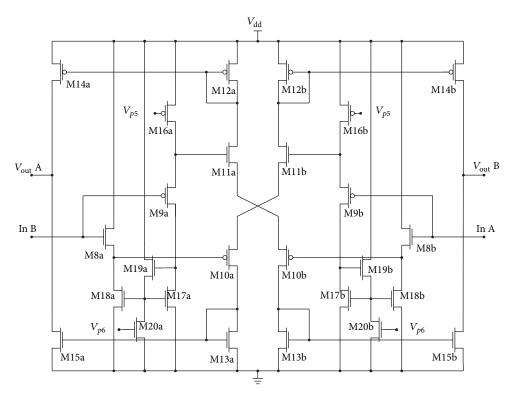

Another successful approach to intrinsically reduce the EMI effects, without adding any kind of filter, is presented in [34] and is based on the design of strongly symmetrical topologies. The symmetrical topology proposed in [34] is based on two identical fully differential source cross-coupled amplifiers, combined in cascade connection in order to achieve a large gain. The circuital scheme is shown in Figure 7. This topology is very useful when the output slew rate of the OpAmp is an important task; moreover, such a scheme leads to a strong symmetry of the output voltage thanks to the mirrored path of the signals. Indeed, as shown in Figure 7, the input voltages are applied to the gates of both M2a and M2b, in order to bias the NMOS differential pair, and to the gates of M1a and M1b to bias the PMOS differential pair.

NMOS and PMOS differential pairs are connected with cross-coupled sources. Hence, the input voltages are symmetrically applied to the gates of the 2nd differential pairs M3 and M4

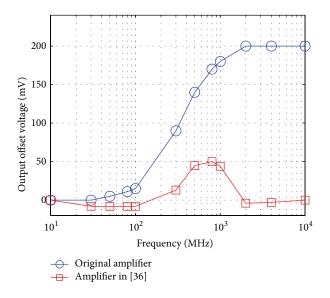

Thus, any voltage mismatch, due to stray elements and nonidealities, is removed by this cross-connection. This leads to a very symmetrical path for both signals across the amplifier and to an EMI immunity more than 2 orders of magnitude increased, as clearly demonstrated by the plot in Figure 8 where the EMI induced offset is compared to that of the uA741.

The architecture proposed in [34] is unfortunately not suited for the ultralow voltage supply of current integrated circuits. This is mainly due to the complex cascode connections.

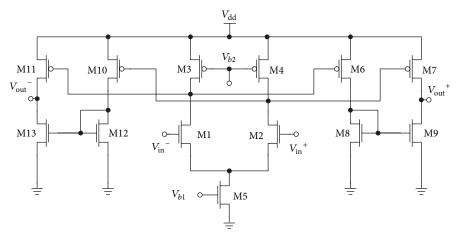

Therefore, an alternative solution is proposed derived from the Miller amplifier [35]. The overall schematic is shown in Figure 9.

Finally, a circuit that enhances the EMI immunity of amplifiers by deleting the common mode signals has been recently proposed. The EMI induced voltage generated at the output of the input stage  $V_{\rm os}$  is indeed due to the differential and the common mode signals  $V_{\rm dm}$  and  $V_{\rm cm}$ , as calculated in the following mathematical expression:

$$= \frac{\int_{-\infty}^{\infty} \left| H_{\rm cm} \left( j\omega \right) \cdot V_{\rm cm} \left( j\omega \right) \cdot V_{\rm dm} \left( j\omega \right) \right| \cdot \cos \phi \cdot d\omega}{V_{\rm GS1.2} - V_t}.$$

(1)

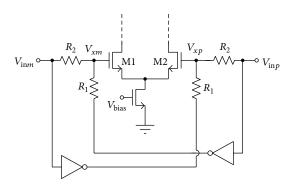

In a differential amplifier, the differential signals cannot of course be removed, but the common mode components can be deleted. The schematic of the common mode cancellation circuit proposed in [36] is shown in Figure 10. If the circuit is properly sized (by choosing the right value of the resistors) the common mode signals are cancelled while the differential signals are doubled.

Consequently, the resulting EMI susceptibility is reduced, as plotted in Figure 11, where the offset is compared between the original amplifier and the one modified by including the common mode cancellation stage.

### 4. Design of High EMI Immunity Voltage Reference

It is well established that analog CMOS circuit design relies on close geometry matching of components which yields precise ratios of component values. As this applies only to a lateral geometry defined within the same mask, only related components (i.e., components of the same nature, so to speak) can be well matched. On the contrary, the definition of absolute values and tolerances is rather poor, as it depends on various material properties and technology processing steps. Nevertheless, absolute reference values are often needed. The on-chip reference generation is usually confined to voltage reference generation using the bandgap principle, which utilizes parasitic pnp-bipolar transistors of a CMOS process for this purpose.

It is worth adding that, in the literature, much attention is paid to many quality aspects, such as the mean relative temperature dependency and the accuracy, but the influence of electromagnetic interferences is only recently treated explicitly.

In order to reach a clear comprehension of the EMI on a bandgap reference circuit, it should be pointed out that in many applications analog and digital subsystems are required to coexist on the same chip, sharing the same power sources. In such a system, electromagnetic interferences may arise from external circuits and from subsystems integrated on the same die, spreading through the supply lines leading to large unexpected fluctuations of the power supply, as illustrated in Figure 12.

In order to investigate the EMI effects on bandgap references, the interferences are modelled by means of spurious signals applied to the power pins. As already stated, EMIs are represented by means of undamped sinusoidal waveforms that allow for an easy measurement in laboratory.

FIGURE 7: Highly symmetrical fully differential source cross-coupled amplifier proposed in [34].

FIGURE 8: Measured EMI induced offset: a comparison between the uA741 and the amplifier proposed in [34], in the case of  $1V_p$  EMI signal.

Among the various voltage reference architectures, the most popular circuit is the bandgap reference based on pn junctions, OpAmp, and ratioed resistors [37]. On the other hand, in order to meet the important constraints of low power supply voltage and low power dissipation, it is desirable

to use simple architectures, avoiding operational amplifiers and additional circuits. Therefore, many different bandgap architectures were also designed [38].

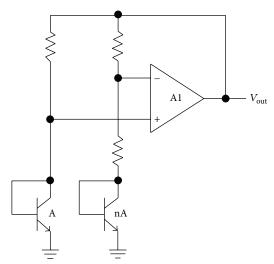

The first considered reference is the "Brokaw" circuit, shown in Figure 13 [37]: an improved version, widely used in recent ICs, is often called "Kuijk bandgap" [39] and it is based on ratioed resistors and OpAmp, along with the parasitic bipolar pnp transistors provided by the CMOS technology.

For Brokaw and Kuijk bandgap circuits, a few topologies can be found in the literature [40–44], showing a low EMI susceptibility. Here, the basic topology is often improved by enhancing the EMI immunity of the operational amplifier, following the approaches depicted in Section 3, by changing the bandgap bias current and by introducing filter capacitors. Layout and technological techniques to reduce the coupling between the power supply net and the poly resistors are also useful to increase the immunity to electromagnetic interferences [40].

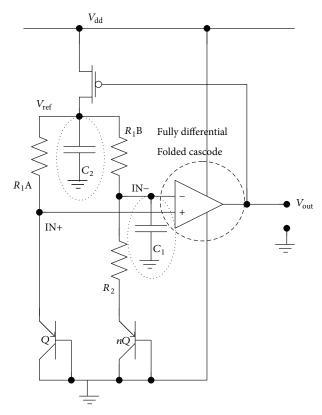

In Figure 14 an example of a high EMI immunity bandgap voltage reference is shown, based on the solution proposed in [44].

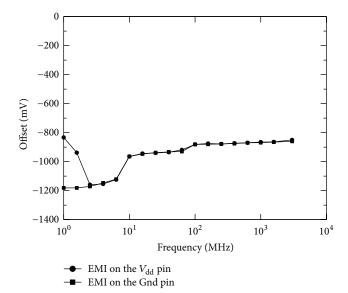

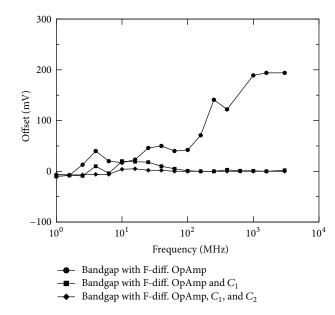

As investigated in [44], the original CMOS voltage reference, designed in AMS CXQ 0.8  $\mu$ m process, was very susceptible to the  $1V_p$  interferences arising from the power supply rails, showing a large offset as plotted in Figure 15. To reduce its susceptibility a fully differential folded cascode amplifier with high EMI immunity has been used instead of the single ended Miller amplifier and two capacitors were added on the most critical nodes. The simulated offset of the modified "Kuijk" bandgap is shown in Figure 16. The CMOS

FIGURE 9: Highly symmetrical fully differential amplifier for low voltage supply proposed in [35].

FIGURE 10: The common mode cancellation circuit proposed in [36]: it is used as input stage, to increase the EMI immunity in a Miller differential amplifier.

FIGURE 11: Simulated EMI induced offset: comparison between the original Miller differential amplifier and the one modified by adding the common mode cancellation stage depicted in [36].

FIGURE 12: Scenario of EMI pollution in electronic circuits.

Figure 13: The "Brokaw" voltage reference circuit.

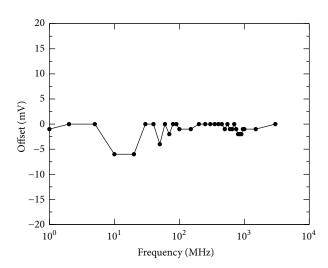

voltage reference has been fabricated in the AMS CXQ 0.8  $\mu$ m process and the test chip was measured, exhibiting a high level of EMI immunity as demonstrated by the measurement results plotted in Figure 17: the offset is indeed several orders of magnitude reduced.

FIGURE 14: Schematic of the EMI-improved "Kuijk" bandgap proposed in [44].

FIGURE 15: Offset of the bandgap voltage references caused by  $1V_p$  EMI signal superimposed to the power supply rails.

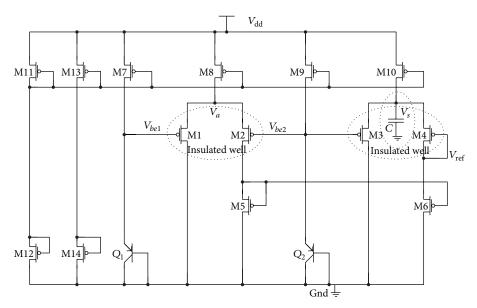

The second considered bandgap topology uses ratioed transistors biased in strong inversion along with the inverse-function technique to produce temperature-insensitive voltage references [45]. With regard to this bandgap topology, analysis and simulations emphasized that the differential

FIGURE 16: Offset of the bandgap circuit modified by using a fully differential amplifier and two capacitors, as shown in the schematic of Figure 14.

FIGURE 17: Measured EMI induced offset of the high-immunity bandgap proposed in [44].

pairs (M1-M2 and M3-M4) play a significant role in EMI susceptibility. Hence, in order to improve the immunity to interferences, M1-M2 and M3-M4 are created in insulated wells and a small capacitor (1 pF) is connected between  $V_s$  and ground. In Figure 18 the schematic of the bandgap circuit modified following this approach is shown. The simulations demonstrated the validity of this approach: considering  $1V_p$  EMI signal superimposed to the supply rails, the maximum induced offset of the original circuit was more than 300 mV while the offset of the modified bandgap is less than 20 mV in the whole frequency range.

FIGURE 18: OpAmp-less and resistorless bandgap circuit with enhanced EMI immunity, presented in [45].

#### 5. Conclusions

In the frame of a higher attention towards the problem of electromagnetic susceptibility, the design of analog circuits widely used in the sensor systems is discussed. In particular, the effect of the electromagnetic interferences is briefly introduced in the most common analog amplifiers and voltage references. Several and recent solutions to increase the EMI immunity are presented: the resulting amplifiers and voltage references exhibit an EMI susceptibility reduced by 2 orders (or even more) of magnitude compared to the classical ones.

#### **Conflict of Interests**

The author declares that there is no conflict of interests regarding the publication of this paper.

#### References

- [1] A. Bababjanyan, H. Melikyan, S. Kim, J. Kim, K. Lee, and B. Friedman, "Real-time noninvasive measurement of glucose concentration using a microwave biosensor," *Journal of Sensors*, vol. 2010, Article ID 452163, 7 pages, 2010.

- [2] C. Hu and S. Hu, "Carbon nanotube-based electrochemical sensors: principles and applications in biomedical systems," *Journal of Sensors*, vol. 2009, Article ID 187615, 40 pages, 2009.

- [3] O. Atalay, W. R. Kennon, and E. Demirok, "Weft-knitted strain sensor for monitoring respiratory rate and its electromechanical modeling," *IEEE Sensors Journal*, vol. 15, no. 1, pp. 110–122, 2015.

- [4] S. Salman, L. Z. Lee, and J. L. Volakis, "A wearable wrap-around sensor for monitoring deep tissue electric properties," *IEEE Sensors Journal*, vol. 14, no. 8, pp. 2447–2451, 2014.

- [5] L. Fanucci, S. Saponara, T. Bacchillone et al., "Sensing devices and sensor signal processing for remote monitoring of vital signs in CHF patients," *IEEE Transactions on Instrumentation and Measurement*, vol. 62, no. 3, pp. 553–569, 2013.

- [6] M. Sakairi, "Water-cluster-detecting breath sensor and applications in cars for detecting drunk or drowsy driving," *IEEE Sensors Journal*, vol. 12, no. 5, pp. 1078–1083, 2012.

- [7] A. M. Cailean, B. Cagneau, L. Chassagne, M. Dimian, and V. Popa, "Novel receiver sensor for visible light communications in automotive applications," *IEEE Sensors Journal*, vol. 15, no. 8, pp. 4632–4639, 2015.

- [8] E. Kampianakis, J. Kimionis, K. Tountas, C. Konstantopoulos, E. Koutroulis, and A. Bletsas, "Wireless environmental sensor networking with analog scatter radio and timer principles," *IEEE Sensors Journal*, vol. 14, no. 10, pp. 3365–3376, 2014.

- [9] J. Segura-Garcia, S. Felici-Castell, J. J. Perez-Solano, M. Cobos, and J. M. Navarro, "Low-cost alternatives for urban noise nuisance monitoring using wireless sensor networks," *IEEE Sensors Journal*, vol. 15, no. 2, pp. 836–844, 2015.

- [10] B. J. Hosticka, "Analog circuits for sensors," in *Proceedings of the 33rd European Solid-State Circuits Conference (ESSCIRC '07)*, pp. 97–102, IEEE, Munich, Germany, September 2007.

- [11] A. Marzuki, Z. A. Abdul Aziz, and A. A. Manaf, "A review of CMOS analog circuits for image sensing application," in Proceedings of the IEEE International Conference on Imaging Systems and Techniques (IST '11), pp. 180–184, Penang, Malaysia, May 2011.

- [12] Y. Hong, T. Liang, T. Zheng et al., "A distance compensated approach used in wireless passive pressure sensor readout system for high temperature application," *Journal of Sensors*, In press.

- [13] O. S. Jahromi and P. Aarabi, "Theory and design of multirate sensor arrays," *IEEE Transactions on Signal Processing*, vol. 53, no. 5, pp. 1739–1753, 2005.

- [14] W. S. Singh, B. P. C. Rao, S. Thirunavukkarasu, and T. Jayakumar, "Flexible GMR sensor array for magnetic flux leakage testing of steel track ropes," *Journal of Sensors*, vol. 2012, Article ID 129074, 6 pages, 2012.

- [15] R. Daly, S. Kumar, G. Lukacs et al., "Cell proliferation tracking using graphene sensor arrays," *Journal of Sensors*, vol. 2012, Article ID 219485, 7 pages, 2012.

- [16] J. Long, A. He, A. Liu, and X. Chen, "Adaptive Sensing with reliable guarantee under white Gaussian noise channels of sensor networks," *Journal of Sensors*, vol. 2015, Article ID 532045, 21 pages, 2015.

- [17] M. Ramdani, E. Sicard, A. Boyer et al., "The electromagnetic compatibility of integrated circuits—past, present, and future," *IEEE Transactions on Electromagnetic Compatibility*, vol. 51, no. 1, pp. 78–100, 2009.

- [18] I. Chahine, M. Kadi, E. Gaboriaud, A. Louis, and B. Mazari, "Characterization and modeling of the susceptibility of integrated circuits to conducted electromagnetic disturbances up to 1 GHz," *IEEE Transactions on Electromagnetic Compatibility*, vol. 50, no. 2, pp. 285–293, 2008.

- [19] V. Ceperic and A. Baric, "Modelling of electromagnetic immunity of integrated circuits by artificial neural networks," in *Proceedings of the 20th International Zurich Symposium on Electromagnetic Compatibility*, pp. 373–376, IEEE, Zürich, Switzerland, January 2009.

- [20] I. Gil and R. Fernández-Garcia, "Characterization and modelling of EMI susceptibility in integrated circuits at high frequency," in *Proceedings of the IEEE International Symposium* on Electromagnetic Compatibility (EMC EUROPE '12), pp. 1–6, IEEE, Rome, Italy, September 2012.

- [21] J.-M. Redouté and M. Steyaert, *EMC of Analog Integrated Circuits*, Springer, Dordrecht, The Netherlands, 2010.

- [22] C. R. Paul, *Introduction to Electromagnetic Compatibility*, John Wiley & Sons, 1992.

- [23] A. S. Poulton, "Effect of conducted EMI on the DC performance of operational amplifiers," *Electronics Letters*, vol. 30, no. 4, pp. 282–284, 1994.

- [24] G. Masetti, S. Graffi, D. Golzio, and Z. M. Kovács-V, "Failures induced on analog integrated circuits by conveyed electromagnetic interferences: a review," *Microelectronics Reliability*, vol. 36, no. 7-8, pp. 955–972, 1996.

- [25] G. Setti and N. Speciale, "Design of a low EMI susceptibility CMOS transimpedance operational amplifier," *Microelectronics Reliability*, vol. 38, no. 6–8, pp. 1143–1148, 1998.

- [26] F. Fiori, "Operational amplifier input stage robust to EMI," *Electronics Letters*, vol. 37, no. 15, pp. 930–931, 2001.

- [27] C. Walravens, S. Van Winckel, J. M. Redouté, and M. Steyaert, "Efficient reduction of electromagnetic interference effects in operational amplifiers," *Electronics Letters*, vol. 43, no. 2, pp. 84– 85, 2007.

- [28] J.-M. Redouté and M. Steyaert, "EMI resisting CMOS differential pair structure," *Electronics Letters*, vol. 42, no. 21, pp. 1217–1218, 2006.

- [29] J.-M. Redouté and M. S. Steyaert, "EMI-resistant CMOS differential input stages," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 57, no. 2, pp. 323–331, 2010.

- [30] F. Fiori and P. S. Crovetti, "Complementary differential pair with high immunity to RFI," *Electronics Letters*, vol. 38, no. 25, pp. 1663–1664, 2002.

- [31] A. Richelli, "CMOS OpAmp resisting to large electromagnetic interferences," *IEEE Transactions on Electromagnetic Compatibility*, vol. 52, no. 4, pp. 1062–1065, 2010.

- [32] B. Subrahmanyam, D. Das, M. Shojaei-Baghini, and J.-M. Redoute, "A balanced CMOS OpAmp with high EMI immunity," in Proceedings of the International Symposium on Electromagnetic Compatibility (EMC Europe '14), pp. 703–708, Gothenburg, Sweden, September 2014.

[33] A. Richelli, G. Matig-a, and J.-M. Redouté, "Design of a folded cascode opamp with increased immunity to conducted electromagnetic interference in 0.18 µm CMOS," *Microelectronics Reliability*, vol. 55, no. 3-4, pp. 654–661, 2015.

- [34] A. Richelli, L. Colalongo, and Z. M. Kovacs-Vajna, "Increasing the immunity to electromagnetic interferences of CMOS OpAmps," *IEEE Transactions on Reliability*, vol. 52, no. 3, pp. 349–353, 2003.

- [35] A. Richelli, "CMOS OpAmp resisting to large electromagnetic interferences," *IEEE Transactions on Electromagnetic Compatibility*, vol. 52, no. 4, pp. 1062–1065, 2010.

- [36] A. Richelli and J.-M. Redouté, "Increasing the EMI immunity of CMOS operational amplifiers using an on-chip common-mode cancellation circuit," in *Proceedings of the IEEE EMC Europe Conference*, pp. 698–702, IEEE, Gotheborg, Sweden, September 2014.

- [37] J. Hu, Y. Yin, and H. Deng, "Design of a high-performance Brokaw band-gap reference," in *Proceedings of the International Conference on Anti-Counterfeiting Security and Identification in Communication (ASID '10)*, pp. 126–129, IEEE, Chengdu, China, July 2010.

- [38] A. E. Buck, C. L. McDonald, S. H. Lewis, and T. R. Viswanathan, "A CMOS bandgap reference without resistors," *IEEE Journal of Solid-State Circuits*, vol. 37, no. 1, pp. 81–83, 2002.

- [39] K. E. Kuijk, "A precision reference voltage source," *IEEE Journal of Solid-State Circuits*, vol. 8, no. 3, pp. 222–226, 1973.

- [40] N. Montemezzo, E. Orietti, S. Buso, G. Meneghesso, A. Neviani, and G. Spiazzi, "A discussion of the susceptibility of a Brokaw bandgap to EMI," in *Proceedings of the IEEE International Symposium on Electromagnetic Compatibility (EMC '06)*, pp. 796–801, August 2006.

- [41] E. Orietti, N. Montemezzo, S. Buso, G. Meneghesso, A. Neviani, and G. Spiazzi, "Reducing the EMI susceptibility of a kuijk bandgap," *IEEE Transactions on Electromagnetic Compatibility*, vol. 50, no. 4, pp. 876–886, 2008.

- [42] J.-M. Redouté and M. Steyaert, "Kuijk bandgap voltage reference with high immunity to EMI," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 57, no. 2, pp. 75–79, 2010.

- [43] S. Yang, P.-I. Mak, and R. P. Martins, "A 104μW EMI-resisting bandgap voltage reference achieving—20dB PSRR, and 5% DC shift undera 4dBm EMI level," in *Proceedings of the IEEE Asia Pacific Conference on Circuits and Systems (APCCAS '14)*, pp. 57–60, IEEE, Ishigaki, Japan, November 2014.

- [44] A. Pretelli, A. Richelli, L. Colalongo, and Z. M. Kovács-Vajna, "Reduction of EMI susceptibility in CMOS bandgap reference circuits," *IEEE Transactions on Electromagnetic Compatibility*, vol. 48, no. 4, pp. 760–765, 2006.

- [45] A. Pretelli, A. Richelli, L. Colalongo, and Z. Kovacs-Vajna, "Robust design of bandgap voltage references with low EMI susceptibility," in *Proceedings of the IEEE Symposium on Elec*tromagnetic Compatibility, pp. 298–302, Arlington, Va, USA, August 2003.

Submit your manuscripts at http://www.hindawi.com